服务热线

一、什么是 CoWoP?

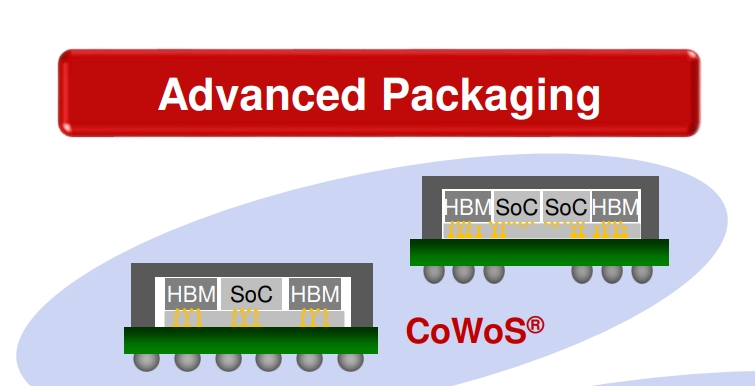

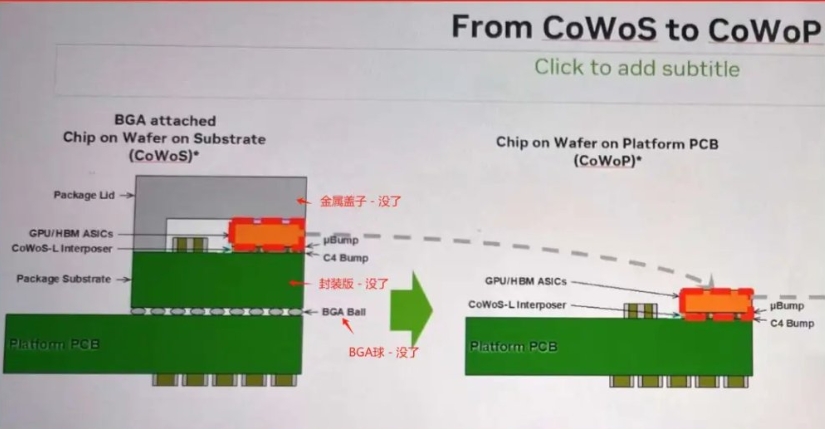

CoWoS(Chip‑on‑Wafer‑on‑Substrate):传统先进的 2.5D 封装,将硅芯片(Logic + HBM)并排贴在一个中介层(硅 Interposer)上,再焊接到封装基板(Package Substrate),然后用 BGA 焊球连接到主板。

CoWoP 的核心思路就是把这个封装基板去掉 —— CoWoP = CoWoS - 封装基板。中介硅片 + 芯片直接安装在增强型主板上,不再走传统封装那一层。

二、为什么这么做?CoWoP 有什么好处

省掉中间层,降低信号损耗

封装基板那层走线、引线、接触都会带来寄生电阻、电容。去掉后,逻辑芯片对高带宽连接(如 NVLink)更可靠、更远、更快。热性能更强

没有封装基板那块厚材料,封装热膨胀系数配合更一致、热堆栈更薄,散热更直接、更好控温,减少板变形(warpage)。成本下降

去掉封装底板和封装盖,少了材料、工艺、BGA焊球等制造步骤,潜在节约封装成本,同时也减轻整体厚度、体积。

三、CoWoP 的关键技术要点

主板(Platform PCB)必须升级

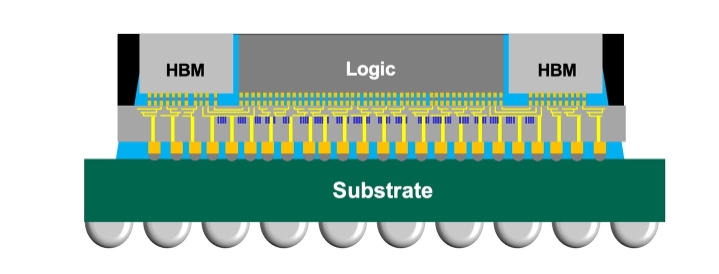

PCB 上要具备过去由封装 substrate 提供的高密度布线能力,包括精准微线距、精准信号/电源/地层布线能力。中介层(Interposer)依然重要

包含 GPU 核心和 HBM 等小 die,放在高精度硅片 interposer 上,保持高带宽连接能力。可靠力学与热匹配设计

硅 interposer、die 与 PCB 的热膨胀系数(CTE)必须匹配,避免因热循环导致 warpage 或失效。信号电气完整性管理

PCB 与 interposer 对高速信号(如 NVLink、HBM RDL)路径需要严格控制阻抗、延迟、电容、电感分布。

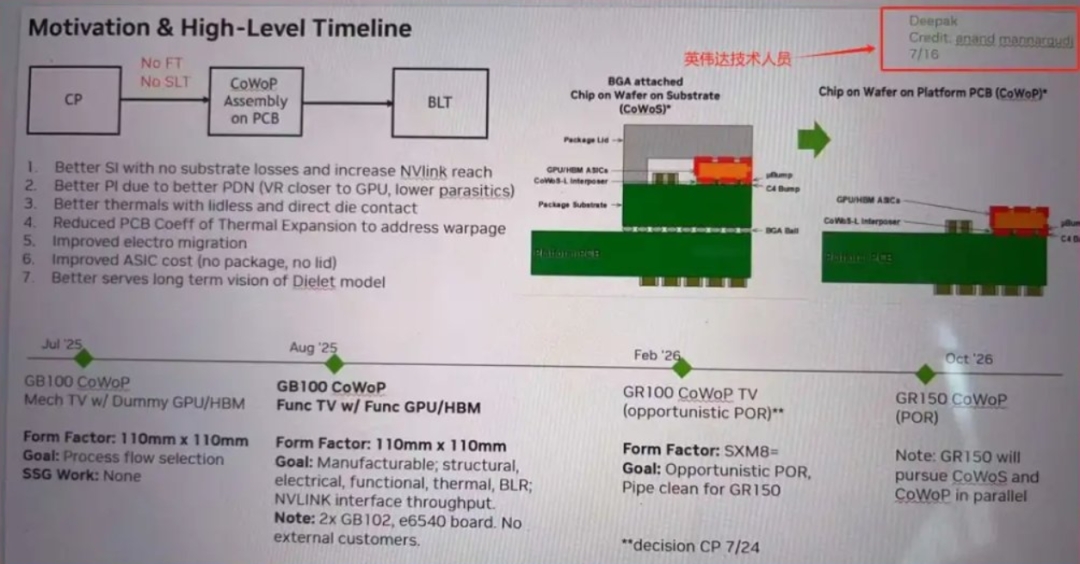

四、NVIDIA 的 CoWoP 规划与时间节点

自 2025 年 7 月 起,NVIDIA 在内部进行 GB100 的 CoWoP 机械样板测试(含 Dummy GPU/HBM),尺寸约 110 mm × 110 mm。

2025 年 8 月 将进行结构、电气、热性能和 NVLink 带宽验证。

2026 年 2 月 开启 GR100 CoWoP 功能验证,接着在 2026 年 10 月 推出 GR150 助力并行 CoWoS 与 CoWoP 路线。

五、系统流程概览(从传统到 CoWoP)

CoWoP 是在先进 AI 封装中,去掉了封装基板这一层,把 die + interposer 直接贴到平台 PCB 上,借力 PCB 本身承接 substrate 功能,让信号更快、热阻更小、成本更低,但要求 PCB、设计和热机械一体化的集成度非常高。

六、 CoWoP(Chip‑on‑Wafer‑on‑Platform) 对半导体产业链的影响:

1、封装模式变革:需求迁移与供应链重构

从 CoWoS‑S 向 CoWoS‑L 或 CoWoP 的转变,意味着对封装基板层的大幅调整。NVIDIA 正逐渐减少 CoWoS‑S 订单,集中资源投入 CoWoS‑L 与 CoWoP,以支撑 Blackwell 系列高性能 AI GPU 的发展 。

TSMC 的 CoWoS 能力长期供不应求,CoWoP 的推广可能部分缓解这一瓶颈,特别是若 CoWoP 能有效替代部分 CoWoS-S 产能需求 。

同时,NVIDIA 开始寻求与 UMC、Intel、Amkor、ASE 等合作伙伴合作,建立多元化的封装供应链,减轻对 TSMC 独占 CoWoS 的依赖。

2、对封装、PCB、PCB 材料与制造合作伙伴的挑战

CoWoP 将封装 substrate 功能迁移到平台 PCB,这要求 PCB 厂商升级生产工艺:更细线距、高密度线路、多层电源地层、低热膨胀系数材料等。

原先制作封装 substrate 的企业,如 Amkor、ASE、SPIL,在 CoWoP 时代需调整定位,可能转向更多 interposer 的测试与组装环节,或扩展业务至高精度 PCB 领域。

3、封装供应商与功耗相关链条的重新布局

传统 CoWoS substrate 供应商业务可能减少,而 提供硅中介层(interposer)的厂商需求将持续增长。

HBM 高带宽内存供应商(如 SK Hynix、Samsung)由于 CoWoP 依然使用 HBM,与封装 interposer 集合,因此对 HBM 的依赖继续强化,市场需求和价格仍上涨趋势明显。

4、研发挑战与联盟协同升级

CoWoP 要求 PCB 与 interposer、die 一体设计,信号、电源、热管理、机械力学需协同工程化实现。这推动 设计工具商、EDA、材料商、PCB 厂商共研新规范。

封装技术更新加快,CoWoP 与 CoWoS‑L、FOPLP(扇出面板级封装)形成互补和竞争。这对封装厂商提出更高要求,也创造新的合作空间 。

5、产业链整体影响概览

| GPU 芯片厂商(NVIDIA、AMD) | |

| TSMC / UMC | |

| 封装厂商(Amkor、ASE、Intel Packaging) | |

| PCB 厂商 / 材料商 | |

| HBM 供应商 | |

| 整体行业生态 |

6、小结一句话

CoWoP 带来的最核心影响是:将封装 substrate 的功能重置到主板层,推动 PCB 制造商、设计工具、材料供应商与传统封装厂商重新协作,重构 AI 封装与供应链生态。 它不仅可能缓解 CoWoS 的产能瓶颈,还将推动封装与板级供应链迈向更高集成度和设计协同性时代。

免责声明:本文采摘自“老虎说芯”,本文仅代表作者个人观点,不代表萨科微及行业观点,只为转载与分享,支持保护知识产权,转载请注明原出处及作者,如有侵权请联系我们删除。

粤公网安备44030002007346号

粤公网安备44030002007346号